Détails logiciels:

Version: 5.20.1

Date de transfert: 20 Feb 15

Développeur: Dolphin Integration

Licence: Gratuit

Popularité: 111

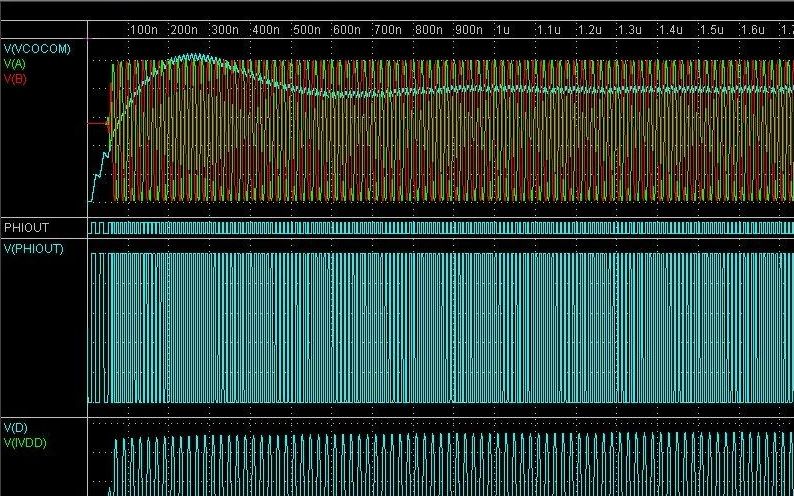

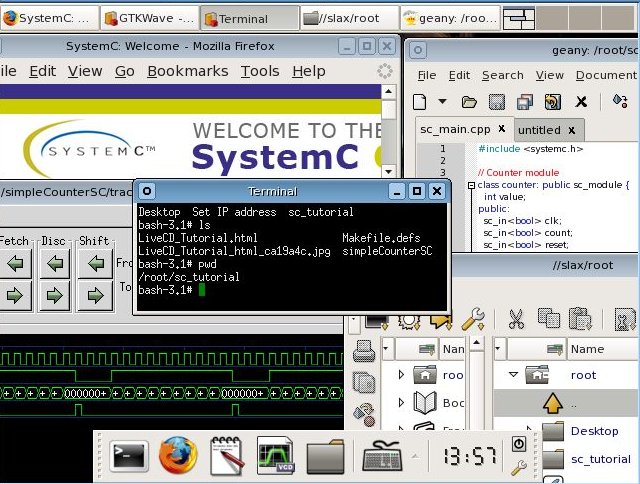

Dolphin Smash est un signal mixte et multi-langue simulateur gratuit pour les PCB et les conceptions de circuits intégrés. Il étend ses capacités de signal mixte sensibilité-analyse et couverture de code, afin d'identifier les faiblesses de circuit pour le concepteur conscients DfM et de détecter des failles dans Bancs de test virtuels.

Ce qui est nouveau dans cette version:

- Cette version améliore l'exécution de chargement de gros fichiers Verilog avec un nombre important de ports et met en œuvre le soutien de la directive .malias assigner un alias à un modèle ou nom du sous-circuit, avec un certain nombre de corrections mineures.

Ce qui est nouveau dans la version 5.19.0:

- Cette version met en œuvre des améliorations majeures à l'instanciation des modèles de comportement (HDL / HDL-AMS) dans netlists SPICE avec macro-modèles mixtes, de meilleures capacités multi-threading pour augmenter la vitesse de simulation transitoire de conceptions analogiques, Monte Carlo et de balayage des analyses sur la logique des conceptions, une visionneuse de coloration de domaine avec la phase et l'amplitude visualisation,. Modèle pour les modèles Verilog-A fonderie, .NRT pour vérifier entre les formes d'onde équivalence, et la possibilité de définir un répertoire de rediriger tous les fichiers de sortie.

Quoi de neuf dans la version 5.18.0:

- Cette version met en œuvre des améliorations majeures parmi lesquelles domaine coloration pour une première approximation du pôle / zéro endroits, une directive .PZ pour la pole / analyse zéro, support des fichiers .wav que ouput de modèles logiques et des fonctions de traitement d'extraction de segmentation CSC.

Quoi de neuf dans la version 5.17.0:

- Cette version met en œuvre des améliorations majeures notamment étendu Assertion Based- Vérification (ABV) capacités avec SystemVerilog Assertions (SVA), le respect de Verilog-AMS wreal pour le Real Valued Modeling (RVM), l'augmentation de Verilog-HDL et Verilog-A le respect de la langue, une meilleure compatibilité avec HSpice .IF, .ELSIF, .ELSE, .ENDIF conditionnelle générer des instructions, et accéléré le chargement du circuit, Monte Carlo et de balayage analyse.

Ce qui est nouveau dans la version 5.16.2:

- Cette version offre une augmentation significative de la vitesse pour le chargement des fichiers de bibliothèque de SPICE et circuits, en particulier les fichiers importants lors de l'accès sur lentes disques réseau.

- Un certain nombre d'améliorations et de corrections mineures ont également été faites.

Qu'est-ce que de nouveaux dans la version 5.15.2:

- Un certain nombre de défauts ont été corrigés et quelques améliorations mineures ont été mis en œuvre.

Ce qui est nouveau dans la version 5.15.1:

- SMASH - Viewer:

- Améliorations:

- Ajout d'un menu pour «plier tous» et «se dérouler tous les« éléments dans l'éditeur de texte (DDIsa05778 - SMASH 5.15.0).

- Ajout d'une option dans le & quot; & quot Ajouter traces; dialogue permettant de tracer des vecteurs logiques valeurs non signés dans les graphes analogiques (DDIsa05953 - SMASH 5.15.0).

- Ajout clic droit entrée de menu dans le panneau de circuit permettant de supprimer circuits récentes (DDIsa05981 - SMASH 5.15.0).

- Ajout d'entrées de menu pour afficher / masquer volets gauche et bas qui ne pouvaient auparavant être fait en double-cliquant sur le

- répartiteurs (DDIsa06032 - SMASH 5.15.1).

- mis en œuvre l'exportation de l'installation de l'application dans le répertoire de circuit et l'édition de circuit con fi guration avec la boîte de dialogue des préférences (DDIsa06034 - SMASH 5.15.1).

- Mise en œuvre la possibilité d'associer un script Tcl avec un circuit pour enregistrer des fonctions de circuit spéci fi ques de crochet (DDIsa06098 - SMASH 5.15.1).

- Amélioration de la gestion du contrôle simulateur fi le des mises à jour de sorte que la fi d'origine ne est pas endommagé le moment il n'y a pas d'espace libre sur

- disque (DDIsa06209 - SMASH 5.15.1) .

- Modi fi cations:

- Modi fi ed manipulation de dialogue FFT de permettre spéci fi cation d'un temps négatif (DDIsa04663 - SMASH 5.15.0) .

- Modi fi ed SMASH intégré accumulation de vin sous Linux pour supprimer de nombreux messages d'erreur lors de l'exécution Xlib émis

- affiché sur un serveur Cygwin X (DDIsa05532 - SMASH 5.15.0) .

- Mise en œuvre une température de défaut égal à 25 degC lorsque le HSPICE fl avor est sélectionné (DDIsa05790 - SMASH 5.15.0).

- Modi fi é génération d'exploitation point fi chier sorte que les données de la logique liée ne est pas sortie par défaut et peut être activée via

- les préférences de l'application (DDIsa05154 - SMASH 5.15.1).

- Modi fi é le paramètre «OP» des directives de la .AC »et« .NOISE 'qui devrait avoir la même valeur par défaut (DDIsa06037 - SMASH 5.15.1).

- Correction embeddedWinelib pour permettre le chargement fi avec les noms de chemins très longs sous Linux (DDIsa06193 - SMASH 5.15.1).

- Bug fi xing:

- version de Wine corrigée de SMASH afin d'être en mesure de charger circuits nécessitant plus de 600 Mb de mémoire allouée (DDIsa05525 - SMASH 5.15.0).

- Correction de l'affichage des quantités VHDL-AMS internes Dans le dialogue Ajouter de trace (DDIsa06096 - SMASH 5.15.1).

- manutention Correction de la directive «.trace» qui ne devrait pas être sensible à la casse sur la forme d'onde 'ONOISE' au cours d'une analyse du bruit (DDIsa06106 - SMASH 5.15.1).

- corrigée exportation de fi chiers audio de la & quot; Fichier Audio ... & quot; dialogue qui a été avorter avec un message d'erreur (DDIsa06117 - SMASH 5.15.1) .

- Correction SNR et THD calculs lorsqu'elle est effectuée dans une fenêtre générique de .fft résultats fi chier (DDIsa06192 - SMASH 5.15.1).

- Correction de la manipulation signaux FFT du * .fft.amf dans des fenêtres génériques afin qu'ils soient serrés à -400dB lieu de -300dB (DDIsa06240 - SMASH 5.15.1).

- Correction de la manipulation mise à jour chèque qui pourrait causer SMASH crash en présence d'un changement entrée vide (DDIsa06242 - SMASH 5.15.1).

- Correction superposition de forme d'onde qui a été désactivée pour les simulations logiques (DDIsa06258 - SMASH 5.15.1) .

- Correction de l'affichage des valeurs de Tera (DDIsa06264 - SMASH 5.15.1).

- SMASH - Lot:

- Améliorations:

- Mise en œuvre la possibilité d'associer un script Tcl avec un circuit pour enregistrer des fonctions de circuit spéci fi ques de crochet (DDIsa06098 - SMASH 5.15.1).

- Modi fi cations

- Correction embeddedWinelib pour permettre le chargement fi avec les noms de chemins très longs sous Linux (DDIsa06193 - SMASH 5.15.1).

- Bug fi xing:

- version de Wine corrigée de SMASH afin d'être en mesure de charger circuits nécessitant plus de 600 Mb de mémoire allouée (DDIsa05525 - SMASH 5.15.0).

- SMASH - Kernel

- Améliorations:

- Ajout du support de la directive '.Option TNOM = val' pour la compatibilité avec HSPICE (DDIsa05531 - SMASH 5.15.0).

- Mise en œuvre la manipulation de modèles C-Logic en utilisant le modèle de simulation binaire (BSM) la technologie en interne (DDIsa05602 - SMASH 5.15.0).

- Mise en œuvre du soutien de point-virgule ';' comme caractère de commentaire en ligne pour la PSPICE fl avor (DDIsa05769 - SMASH 5.15.0).

- Amélioration de l'extraction DC utilisé par la FFT (DDIsa05774 - SMASH 5.15.0).

- Mise en œuvre une température de défaut égal à 25 degC lorsque le HSPICE fl avor est sélectionné (DDIsa05790 - SMASH 5.15.0).

- accéléré le chargement des aplati netlists SPICE (DDIsa05791 - SMASH 5.15.0).

- Ajouté & quot; lang = & quot; option de la directive .LIB afin de permettre spécifiant le langage de description de matériel (DDIsa05895 - SMASH 5.15.0).

- 30 Septembre 2010 Page 10 / 23SMASH 5.15.1, SCROOGE 2.4.1 et 5.15.1 SHAKER Nouvelles fonctionnalités

- Mise en œuvre améliorée analyse SPICE pour accélérer l'analyse et fournir de meilleurs rapports d'erreur, y compris le fi et numéros de ligne (DDIsa01619 - SMASH 5.15.1).

- Amélioration de la convergence pour certains modèles PSpice en améliorant la détection des non fi nis (NAN) valeurs au cours du point de fonctionnement et analyse transitoire (DDIsa03199 - SMASH 5.15.1).

- Mise en œuvre de l'analyse SPICE des directives .include dans les sous-circuits de compatibilité HSPICE (DDIsa04326 - SMASH 5.15.1).

- Mise en œuvre de l'analyse SPICE des directives .LIB dans les sous-circuits de compatibilité HSPICE (DDIsa05538 - SMASH 5.15.1).

- Gestion Mise en œuvre des préférences par circuit con fi guration (DDIsa06035 - SMASH 5.15.1).

- Mise en œuvre la possibilité d'associer un script Tcl avec un circuit pour enregistrer des fonctions de circuit spéci fi ques de crochet (DDIsa06098 - SMASH 5.15.1).

- Amélioration de la gestion du contrôle simulateur fi le des mises à jour de sorte que la fi d'origine ne est pas endommagé le moment il n'y a pas d'espace libre sur le disque (DDIsa06209 - SMASH 5.15.1).

- Modi fi cations:

- Modi fi ed manipulation des simulations analogiques pour arrêter simulations lorsque les données de forme d'onde ne peuvent pas être écrites dans les fi binaire, pour

- exemple lorsque aucun espace disque si disponible (DDIsa05907 - SMASH 5.15.0).

- Changed un message d'erreur à un message d'avertissement lorsque la méthode de convergence PowerUp échoue lors d'une analyse du point de fonctionnement (DDIsa05980 - SMASH 5.15.0).

- Modi fi é les limites pour le kit de SPICE en utilisant l'option de découverte (DDIsa06011 - SMASH 5.15.0).

- Modi fi é génération d'exploitation point fi chier sorte que les données de la logique liée ne est pas sortie par défaut et peut être activé dans les préférences de l'application (DDIsa05154 - SMASH 5.15.1).

- Modi fi ed traitement des signaux logiques dans une hiérarchie de circuit SPICE Verilog raccordement sous-circuits à ne pas créer des dispositifs inutiles d'interface (DDIsa05442 - SMASH 5.15.1).

- Modi fi é le paramètre «OP» des directives de la .AC »et« .NOISE 'qui devrait avoir la même valeur par défaut (DDIsa06037 - SMASH 5.15.1).

- Modi fi ed manipulation des descriptions logiques compilées de sorte que le BSM intermédiaire fi ls peut être insérée quand le code source Verilog ne est pas disponible (DDIsa06186 - SMASH 5.15.1).

- Correction embeddedWinelib pour permettre le chargement fi avec les noms de chemins très longs sous Linux (DDIsa06193 - SMASH 5.15.1).

- Gestion optimisée de blocage multiples assigne un signal dans le même delta cycle (DDIsa06281 - SMASH 5.15.1).

- Bug fi xing:

- Gestion Correction de Spice à Verilog instanciation lors du passage Spice paramètres réels aux paramètres Verilog entières (DDIsa03293 - SMASH 5.15.0).

- Correction du calcul de puissance analogique lorsque les dispositifs SPICE sont directement instanciées de Verilog-A (DDIsa05921 - SMASH 5.15.0).

- Correction du fonctionnement point fi chier sortie lorsque le sélecteur de l'information de l'appareil est réglé sur & quot; ALL informations & quot; (DDIsa05923 - SMASH 5.15.0).

- Correction d'une fuite de mémoire qui se est produite lors de la fermeture d'un circuit avec les directives et .print .PRINTALL dans le contrôle du simulateur fi chier (DDIsa05946 - SMASH 5.15.0).

- VEC_WRITE corrigée qui a été l'ajout de données à la fin de la CVE fi chier quand la simulation a été exécuté plusieurs fois (DDIsa06007 - SMASH 5.15.0).

- Correction d'une fuite de mémoire qui se est produite lors de la fermeture d'un circuit avec les directives de .measure dans le contrôle du simulateur fi chier (DDIsa06008 - SMASH 5.15.0).

- Correction d'une erreur mémoire désallocation lorsqu'une directive .LIB génère une erreur d'analyse qui pourraient causer SMASH de geler (DDIsa06017 - SMASH 5.15.0).

- Correction d'un crash qui pouvait survenir lors de l'analyse du point de fonctionnement des circuits avec des descriptions VHDL-AMS (DDIsa06021 - SMASH 5.15.0).

- Correction VEC_READ véri fi cations de modèles analogiques qui mal quand VOH et les valeurs VOL ne correspond VIH et VIL valeurs (DDIsa06022 - SMASH 5.15.0).

- Correction de l'initialisation de la fonction de modèle de Laplace qui pourrait être incorrecte lors de l'analyse du point de fonctionnement (DDIsa06026 - SMASH 5.15.0) .

- Correction de la manipulation des filets non utilisés dans les descriptions Verilog-A qui ont créé des entrées dans la matrice et ont causé des problèmes de convergence (DDIsa05229 - SMASH 5.15.1).

- Correction de la manipulation TEMPER paramètre automatique lorsque analyses balayage courante (DDIsa05368 - SMASH 5.15.1).

- manutention Correction de la fonction de table qui se est écrasé lorsque les valeurs «x» ne étaient pas dé fi nis dans l'ordre croissant (DDIsa05969 - SMASH 5.15.1).

- Correction du Verilog-A opérateur de Laplace qui pourrait causer des dif fi cultés fi e à un fonctionnement point (DDIsa06027 - SMASH 5.15.1).

- Correction dépendance manipulation de Verilog fi les inclus avec le 'inclure directive qui ont été ignorés par la gestion de la dépendance. (DDIsa06030 - SMASH 5.15.1)

- connexion corrigée de signal logique à un port analogique qui ne était plus la création d'un module d'interface (DDIsa06052 -SMASH 5.15.1).

- Correctedmeasurements sur la petite forme du signal et les fi ajoutée alias formeasure directive fi chier paramètres (DDIsa06065 - SMASH 5.15.1).

- Correction de la manipulation directive .JITTER qui n'a pas été extraite après le rechargement circuit. (DDIsa06080 - SMASH 5.15.1)

- Correction d'un crash qui pouvait survenir lors de l'initialisation d'un Verilog-A signal analogique (DDIsa06097 - SMASH 5.15.1).

- manutention Correction du signal VHDL-AMS DOMAINE qui n'a pas été mis à jour pour l'analyse petit signal quand un operatingpoint ou analyse transitoire a été exécuté première fi (DDIsa06103 - SMASH 5.15.1).

- manutention Correction de la directive «.trace» qui ne devrait pas être sensible à la casse sur la forme d'onde 'ONOISE' au cours d'une analyse du bruit (DDIsa06106 - SMASH 5.15.1).

- Caractéristiques:

- corrigée généré des VCD fi ls qui pourrait être incorrect lorsque les souvenirs ont été retracés (DDIsa06108 - SMASH 5.15.1).

- Correction d'un crash qui se est produite lors de l'exécution d'un multiple analyse du point de fonctionnement en mode batch et en redirigeant la sortie vers un

- fi chier (DDIsa06161 - SMASH 5.15.1) .

- Correction d'économie .fft résultat fi chier quand & quot; moyenne & quot; est activé (DDIsa06171 - SMASH 5.15.1).

- Correction SNR et THD calculs lorsqu'elle est effectuée dans une fenêtre générique de .fft résultats fi chier (DDIsa06192 - SMASH 5.15.1).

- Correction généré CIM fi le nom qui a été enregistré avec un indice hors d'une lors de l'exécution d'une analyse de Monte Carlo (DDIsa06211 - SMASH 5.15.1).

- Corrigé l'affichage d'une mesure DC résultat inattendu fi message d'erreur lorsque le balayage en cours d'exécution et Monte-Carlo analyses (DDIsa06234 - SMASH 5.15.1).

- Correction de la manipulation commentaires en ligne commençant par caractère '$' intérieur de directives (DDIsa06235 - SMASH 5.15.1).

- Correction manutention de dépendance entre le paramètre de caractère et directive .temp (DDIsa06245 - SMASH 5.15.1) .

- Correction SPICE sous-circuit instanciation des descriptions logiques qui pourrait échouer lors de l'instanciation de multiples sous-circuits (DDIsa06248 - SMASH 5.15.1).

- Correction superposition de forme d'onde qui a été désactivée pour les simulations logiques (DDIsa06258 - SMASH 5.15.1) .

- Correction de l'affichage des valeurs de Tera (DDIsa06264 - SMASH 5.15.1).

- Correction de la manipulation netlists de circuits avec des dépendances de la bibliothèque circulaires trouvés dans une bibliothèque c de la fonderie de spéci fi fi ls qui étaient à l'origine d'un accident (DDIsa06276 - SMASH 5.15.1).

- SMASH - SPICE:

- Améliorations:

- Ajout du support de la directive '.Option TNOM = val' pour la compatibilité avec HSPICE (DDIsa05531 - SMASH 5.15.0).

- Mise en œuvre du soutien de point-virgule ';' comme caractère de commentaire en ligne pour la PSPICE fl avor (DDIsa05769 - SMASH 5.15.0).

- Amélioration de l'extraction DC utilisé par la FFT (DDIsa05774 - SMASH 5.15.0).

- accéléré le chargement des aplati netlists SPICE (DDIsa05791 - SMASH 5.15.0).

- Modèle intégré de dispositif de SPICE version PSP 103,1 (DDIsa05936 - SMASH 5.15.0).

- Mise en œuvre améliorée analyse SPICE pour accélérer l'analyse et fournir de meilleurs rapports d'erreur, y compris le fi et numéros de ligne (DDIsa01619 - SMASH 5.15.1).

- Amélioration de la convergence pour certains modèles PSpice en améliorant la détection des non fi nis (NAN) valeurs au cours du point de fonctionnement et analyse transitoire (DDIsa03199 - SMASH 5.15.1).

- Mise en œuvre de l'analyse SPICE des directives .include dans les sous-circuits de compatibilité HSPICE (DDIsa04326 - SMASH 5.15.1).

- Mise en œuvre de l'analyse SPICE des directives .LIB dans les sous-circuits de compatibilité HSPICE (DDIsa05538 - SMASH 5.15.1).

- Ajout du support pour les différents noms qui Verilog-AMS fi les constants.vams et disciplines.vams peuvent avoir (DDIsa06152 - SMASH 5.15.1).

- Modi fi cations:

- Modi fi ed manipulation des simulations analogiques pour arrêter simulations lorsque les données de forme d'onde ne peuvent pas être écrites dans les fi binaire, pour

- exemple lorsque aucun espace disque si disponible (DDIsa05907 - SMASH 5.15.0).

- Changed un message d'erreur à un message d'avertissement lorsque la méthode de convergence PowerUp échoue lors d'une analyse du point de fonctionnement (DDIsa05980 - SMASH 5.15.0).

- Modi fi ed traitement des signaux logiques dans une hiérarchie de circuit SPICE Verilog raccordement sous-circuits à ne pas créer des dispositifs inutiles d'interface (DDIsa05442 - SMASH 5.15.1).

- Modi fi é le paramètre «OP» des directives de la .AC »et« .NOISE 'qui devrait avoir la même valeur par défaut (DDIsa06037 - SMASH 5.15.1).

- Modi fi ed manipulation des sources de bruit pour que le bruit transitoire ne est pas calculé lors de l'analyse de la mise sous tension (DDIsa06221 - SMASH 5.15.1).

- Bug fi xing:

- Gestion Correction de Spice à Verilog instanciation lors du passage Spice paramètres réels aux paramètres Verilog entières (DDIsa03293 - SMASH 5.15.0).

- Correction du calcul de puissance analogique lorsque les dispositifs SPICE sont directement instanciées de Verilog-A (DDIsa05921 - SMASH 5.15.0).

- Correction du fonctionnement point fi chier sortie lorsque le sélecteur de l'information de l'appareil est réglé sur & quot; ALL informations & quot; (DDIsa05923 - SMASH 5.15.0).

- Correction d'une fuite de mémoire qui se est produite lors de la fermeture d'un circuit avec les directives et .print .PRINTALL dans le contrôle du simulateur fi chier (DDIsa05946 - SMASH 5.15.0).

- Correction de la manipulation TEMPER paramètre automatique lorsque analyses balayage courante (DDIsa05368 - SMASH 5.15.1).

- manutention Correction de la fonction de table qui se est écrasé lorsque les valeurs «x» ne étaient pas dé fi nis dans l'ordre croissant (DDIsa05969 - SMASH 5.15.1).

- Correctedmeasurements sur la petite forme du signal et les fi ajoutée alias formeasure directive fi chier paramètres (DDIsa06065 - SMASH 5.15.1).

- Correction de la manipulation directive .JITTER qui n'a pas été extraite après le rechargement circuit. (DDIsa06080 - SMASH 5.15.1)

- Correction de l'analyse de la source pour les paramètres vnoise XSCALE et Yscale et mis à jour la documentation (DDIsa06090 - SMASH 5.15.1) .

- manutention Correction de la directive «.trace» qui ne devrait pas être sensible à la casse sur la forme d'onde 'ONOISE' au cours d'une analyse du bruit (DDIsa06106 - SMASH 5.15.1).

- 30 Septembre 2010 Page 14 / 23SMASH 5.15.1, SCROOGE 2.4.1 et 5.15.1 SHAKER Nouvelles fonctionnalités

- Correction d'analyse de modèle bipolaire paramètre TREF qui a été lu en Kelvin lieu de Celsius (DDIsa06137 - SMASH 5.15.1).

- Correction d'un crash qui se est produite lors de l'exécution d'un multiple analyse du point de fonctionnement en mode batch et en redirigeant la sortie vers un fi chier (DDIsa06161 - SMASH 5.15.1) .

- Correction d'économie .fft résultat fi chier quand & quot; moyenne & quot; est activé (DDIsa06171 - SMASH 5.15.1).

- Correction SNR et THD calculs lorsqu'elle est effectuée dans une fenêtre générique de .fft résultats fi chier (DDIsa06192 - SMASH 5.15.1).

- Correction généré CIM fi le nom qui a été enregistré avec un indice hors d'une lors de l'exécution d'une analyse de Monte Carlo (DDIsa06211 - SMASH 5.15.1).

- Corrigé l'affichage d'une mesure DC résultat inattendu fi message d'erreur lorsque le balayage en cours d'exécution et Monte-Carlo analyses (DDIsa06234 - SMASH 5.15.1).

- Correction de la manipulation commentaires en ligne commençant par caractère '$' intérieur de directives (DDIsa06235 - SMASH 5.15.1).

- Correction manutention de dépendance entre le paramètre de caractère et directive .temp (DDIsa06245 - SMASH 5.15.1) .

- Correction de la manipulation UNIT = paramètre de HERTZ pour les descriptions polynômes dans le modèle de Laplace (DDIsa06255 - SMASH 5.15.1).

- Correction de la manipulation netlists de circuits avec des dépendances de la bibliothèque circulaires trouvés dans une bibliothèque c de la fonderie de spéci fi fi ls qui étaient à l'origine d'un accident (DDIsa06276 - SMASH 5.15.1).

- SMASH - Verilog et Verilog-AMS:

- Améliorations:

- Ajout du support de Verilog-2001 déclarations de paramètres avec la gamme spéci fi cations (DDIsa00671 - SMASH 5.15.0).

- Mise en œuvre de la gestion Verilog & quot; $ dist_ & quot; fonctions du système pour les distributions probabilistes (DDIsa01729 - SMASH 5.15.0).

- Mise en œuvre sémantique véri fi cation pour la tâche Verilog favorable et valeurs transmises sur des arguments (DDIsa01769 - SMASH 5.15.0).

- Mise en œuvre sémantique véri fi cation pour la tâche Verilog favorable et valeurs transmises sur des arguments (DDIsa01872 - SMASH 5.15.0).

- Mise en œuvre utilisation de types entier, réel, en temps réel et d'expression de temps que les arguments de tâches Verilog d'utilisateurs et fonctions (DDIsa02157 - SMASH 5.15.0).

- la détection statique et dynamique ajoutée de l'in fi ni boucles en Verilog & quot; toujours & quot; et & quot; jamais & quot; déclarations contenant uniquement non-bloquante instructions d'affectation (DDIsa02772 - SMASH 5.15.0).

- Mise en œuvre délivrance d'un message d'avertissement lorsque vous utilisez une valeur de type réel au format% d en Verilog $ tâche de système d'affichage (DDIsa02799 - SMASH 5.15.0).

- Ajout du support des déclarations portuaires du module Verilog-2001 dans le style ANSI (DDIsa03035 - SMASH 5.15.0).

- Ajout du support de l'opérateur Verilog-A analogique Laplace (DDIsa03060 - SMASH 5.15.0).

- Gestion Mise en œuvre de résistance spéci fi cations dans Verilog déclarations de signaux (DDIsa03179 - SMASH 5.15.0).

- Mise en œuvre de la gestion Verilog déclarations de variables dans les états de blocs (DDIsa03243 - SMASH 5.15.0).

- Amélioration de l'Verilog analyse des messages d'erreur lors de l'activation d'une fonction non déclarée de l'utilisateur (DDIsa03300 - SMASH 5.15.0).

- Ajout du support de Verilog-2001 & quot; localparam & quot; (déclarations DDIsa03302 - SMASH 5.15.0).

- Mise en œuvre de la gestion Verilog déclarations de variables dans les états séquentiels et parallèles bloc (DDIsa03358 - SMASH 5.15.0).

- Mise en œuvre de délivrer un message d'avertissement lorsque Verilog UDP contient con fl it entrées de la table (DDIsa03473 - SMASH 5.15.0).

- Mise en œuvre de la manipulation Verilog (non) Les missions de blocage avec des retards dans les états intra nommés de blocs (DDIsa03649 - SMASH 5.15.0).

- Amélioration de l'exécution de compilation lors de la déclaration et l'utilisation de plusieurs tâches Verilog utilisateur (DDIsa03780 - SMASH 5.15.0).

- Ajout du support de Verilog-2001 & quot; @ * & quot; (déclarations DDIsa03845 - SMASH 5.15.0).

- management mis en place des expressions de concaténation des valeurs constantes qui sont passés à Verilog tâche ou une fonction (arguments DDIsa03872 - SMASH 5.15.0).

- Ajout du support de Verilog & quot; @ (expression de l'événement) & quot; lorsque l'expression contient des opérateurs (DDIsa04093 - SMASH 5.15.0).

- Mise en œuvre de la manipulation Verilog & quot; »calendrier & quot; directives avec & quot; & quot; 10s et & quot; 100s & quot; unités (DDIsa04112 - SMASH 5.15.0).

- message d'erreur lors de la compilation améliorée émis et en élaborant des modèles Verilog (DDIsa04173 - SMASH 5.15.0).

- la détection statique et dynamique Mise en œuvre des in fi nie boucles en Verilog & quot; jamais & quot; (déclarations DDIsa04253 - SMASH 5.15.0).

- Mise en œuvre instanciation Verilog des réseaux de portes où une connexion est un signal scalaire (DDIsa04689 - SMASH 5.15.0).

- Mise à niveau l'analyseur Verilog intégré pour ouvrir la voie à Verilog 2001, Verilog-AMS 2.3 et SystemVerilog (DDIsa04784 - SMASH 5.15.0).

- Gestion Mise en œuvre lors de la simulation des changements de valeur de retard dans Verilog instructions d'affectation continue (DDIsa04799 - SMASH 5.15.0).

- Ajout du support du bit-sélection et une partie-sélection sur Verilog & quot; & quot entier; variables dans des contextes d'expression de gauche (DDIsa04853 - SMASH 5.15.0).

- Ajout du support du bit-sélection et une partie-sélection sur Verilog & quot; temps & quot; variables dans des contextes d'expression de gauche (DDIsa04854 - SMASH 5.15.0).

- Ajout du support des déclarations portuaires Verilog avec & quot; tri0 & quot; ou & quot; Tri1 & quot; net-types (DDIsa04979 - SMASH 5.15.0).

- Gestion Mise en œuvre des types de données différents mais compatibles pour les expressions passées aux arguments de fonction (Verilog DDIsa05053 - SMASH 5.15.0).

- Amélioration des messages d'erreur lorsque Verilog asymétries de connexion se produisent lors de l'élaboration (DDIsa05640 - SMASH 5.15.0).

- Mise en œuvre de la manipulation Verilog $ tâches d'arrêt et $ système fi nition que les instructions de fonction (DDIsa05743 - SMASH 5.15.0).

- Caractéristiques:

- Mise en œuvre de la manipulation Verilog signaux partiels sélections que les connexions réelles sur les ports de sortie (DDIsa05748 - SMASH 5.15.0).

- Mise en œuvre SDF manutention sur Verilog & quot annotation; $ setuphold & quot; un solde négatif de & quot; configuration & quot; ou & quot; maintenez & quot; valeurs (DDIsa05947 - SMASH 5.15.0).

- Mise en œuvre de manutention en Verilog-A de plusieurs blocs analogiques (DDIsa05984 - SMASH 5.15.0).

- Mise en œuvre délivrer un message d'erreur lorsque vous utilisez un port électrique Verilog gauche-côté de déclaration d'affectation continue (DDIsa05997 - SMASH 5.15.0).

- Ajout du support du mot-clé «signé» dans les déclarations de registre (Verilog DDIsa03766 - SMASH 5.15.1).

- Le support des Verilog délai annotation à l'aide comprimé (gzip) SDF fi ls. (DDIsa05504 - SMASH 5.15.1)

- Le support des paramètres Verilog PATHPULSE $ avec limite de rejet (DDIsa06094 - SMASH 5.15.1).

- Amélioration du traitement des multi-threading pour les descriptions analogiques Verilog-AMS (DDIsa06200 - SMASH 5.15.1).

- Modi fi cations:

- Suppression de la limitation à 32 bits sur les valeurs de paramètres Verilog pour binaire, octal et littéraux hexadécimaux (DDIsa01718 - SMASH 5.15.0).

- Modi fi ed affichage Verilog de la valeur temps qui a été limité à 32 bits et qui permet désormais 64 valeurs de bits (DDIsa02841 - SMASH 5.15.0).

- Modi fi ed Verilog tâche portsmanagement de se comporter comme Verilog tâche variable par rapport à la & quot; automatique & quot; le style (DDIsa03960 - SMASH 5.15.0) .

- Modi fi ed compilation manipulation de modèles Verilog avec un grand (comme 2000) le nombre de déclarations de paramètres qui, auparavant, n'a pas réussi à compiler (DDIsa04122 - SMASH 5.15.0).

- Modi fi ed compilation manipulation de modèles Verilog avec un grand nombre (comme 200 000) des états dans & quot; & quot initiale; ou & quot; toujours & quot;

- blocs qui, auparavant, ne ont pas de compiler (DDIsa04525 - SMASH 5.15.0).

- Modi fi ed manipulation des bibliothèques de modèles Verilog sorte que valide ou non encore supporté modèles ne empêche pas l'utilisation d'autres modèles (DDIsa05604 - SMASH 5.15.0).

- Messages Modi fi ed Verilog sorte que la position de code source où l'erreur se produit peut être affichée avec des liens cliquables (DDIsa05944 - SMASH 5.15.0).

- Modi fi é génération d'exploitation point fi chier sorte que les données de la logique liée ne est pas sortie par défaut et peut être activé dans les préférences de l'application (DDIsa05154 - SMASH 5.15.1).

- Modi fi ed traitement des signaux logiques dans une hiérarchie de circuit SPICE Verilog raccordement sous-circuits à ne pas créer des dispositifs inutiles d'interface (DDIsa05442 - SMASH 5.15.1).

- L'utilisation prolongée des expressions Verilog de sorte qu'ils ne sont pas limités aux valeurs de paramètres (DDIsa06029 - SMASH 5.15.1).

- Ajout d'un lien source manquant dans le message d'erreur émis pour signaler fi chier lors de la déclaration de plusieurs variables Verilog / fils avec le même nom (DDIsa06040 - SMASH 5.15.1).

- Page 17/23 30 Septembre, Caractéristiques 2010new SMASH 5.15.1, SCROOGE 2.4.1 et 5.15.1 SHAKER

- Modi fi ed manipulation de mise en garde concernant l'utilisation de la valeur par défaut Verilog calendrier de sorte qu'il ne est délivré que lorsque le délai est utilisé par le module (DDIsa06050 - SMASH 5.15.1) .

- Modi fi ed manipulation des descriptions logiques compilées de sorte que le BSM intermédiaire fi ls peut être insérée quand le code source Verilog ne est pas disponible (DDIsa06186 - SMASH 5.15.1).

- Amélioration des messages d'erreur en cas Verilog des fonctions du système inconnus, pas pris en charge les fonctions du système et pas pris en charge les styles d'appel (DDIsa06188 - SMASH 5.15.1).

- Gestion optimisée de blocage multiples assigne un signal dans le même delta cycle (DDIsa06281 - SMASH 5.15.1).

- Bug fi xing:

- Correction d'un crash qui se est produit lorsque la déclaration d'entrée un Verilog de redéclaré a été comme un fil de vecteur (DDIsa02987 - SMASH 5.15.0).

- Correction de la vérification en Verilog-A des types d'opérandes mathématiques (DDIsa03019 - SMASH 5.15.0).

- Correction manutention des déclarations avant de signaux (Verilog DDIsa03068 - SMASH 5.15.0).

- a corrigé le soutien en Verilog-A dans des valeurs fi nis à l'intérieur de la gamme de paramètres spéci fi cations (DDIsa03251 - SMASH 5.15.0).

- Gestion Correction de Spice à Verilog instanciation lors du passage Spice paramètres réels aux paramètres Verilog entières (DDIsa03293 - SMASH 5.15.0).

- Correction de la manipulation Verilog valeur constante 2147483648 qui, auparavant, n'a pas réussi à compiler (DDIsa03746 - SMASH 5.15.0).

- Correction d'un plantage qui pouvait se produire en raison d'une exception non interceptée dans un modèle Verilog (DDIsa03931 - SMASH 5.15.0).

- Correction d'une erreur de compilation quand un argument de sortie de la tâche Verilog est passé à une sous-tâche permettant (DDIsa03963 - SMASH 5.15.0).

- Correction de la manipulation analyse de couverture avec des expressions contenant Verilog logiques et réels arguments (DDIsa05199 - SMASH 5.15.0).

- évaluation corrigée de Verilog expressions de réplication où la constante est zéro (DDIsa05227 - SMASH 5.15.0).

- Correction manutention des déclarations avant de variables (Verilog DDIsa05232 - SMASH 5.15.0).

- Correction d'un crash qui se est produite en Verilog-A lors de l'utilisation d'un tableau d'entrée dans une fonction analogique. (DDIsa05431 - SMASH 5.15.0)

- Correction de la manipulation des valeurs négatives pour les gammes Verilog portuaires (DDIsa05520 - SMASH 5.15.0).

- Correction du calcul de puissance analogique lorsque les dispositifs SPICE sont directement instanciées de Verilog-A (DDIsa05921 - SMASH 5.15.0).

- Correction cession de Verilog paramètres réels à VHDL génériques entiers dont la valeur a été tronquée au lieu d'arrondi (DDIsa05948 - SMASH 5.15.0).

- Correction du comportement Verilog MOS passe afin qu'ils propagent la force d'entrée change même si aucun périphérie se produit (DDIsa05949 - SMASH 5.15.0).

- Caractéristiques:

- Correction du comportement Verilog & quot; $ attente & quot; et & quot; $ Recouvrement & quot; moment-contrôle des fonctions qui pourraient signaler mauvaises violations à la simulation initialisation (DDIsa05993 - SMASH 5.15.0).

- Correction du nom de primitives SPICE isine et vsine qui ne ont pas chargé comme décrit dans le LRM (DDIsa06009 - SMASH 5.15.0).

- Correction de l'initialisation de la fonction de modèle de Laplace qui pourrait être incorrecte lors de l'analyse du point de fonctionnement (DDIsa06026 - SMASH 5.15.0) .

- Correction déclenchement de la sensibilité sur les variables Verilog assignées à plusieurs reprises dans un delta-seul cycle (DDIsa04932 - SMASH 5.15.1).

- Correction de la manipulation des filets non utilisés dans les descriptions Verilog-A qui ont créé des entrées dans la matrice et ont causé des problèmes de convergence (DDIsa05229 - SMASH 5.15.1).

- Correction du Verilog-A opérateur de Laplace qui pourrait causer des dif fi cultés fi e à un fonctionnement point (DDIsa06027 - SMASH 5.15.1).

- Correction dépendance manipulation de Verilog fi les inclus avec le 'inclure directive qui ont été ignorés par la gestion de la dépendance. (DDIsa06030 - SMASH 5.15.1)

- Améliorations:

- Caractéristiques:

- Améliorations:

- Améliorations:

- Améliorations:

- Caractéristiques:

Commentaires non trouvées